# EECE7248 Lab Tutorial: Common-Source Amplifier Layout

#### Gyunam Jeon, Yixuan He, Yong-Bin Kim

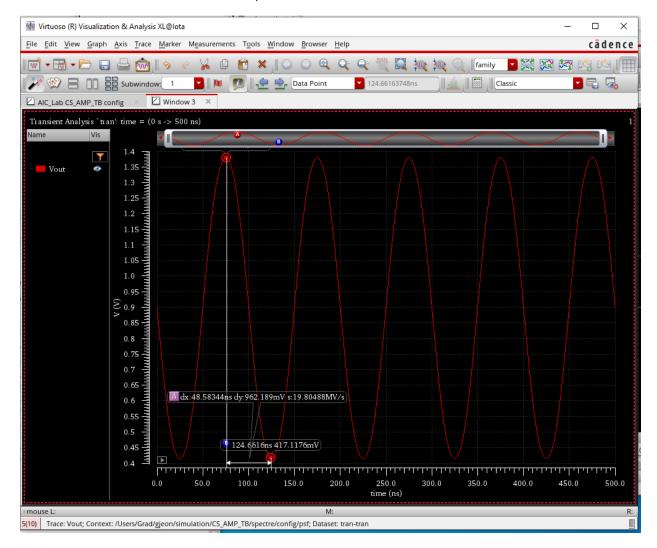

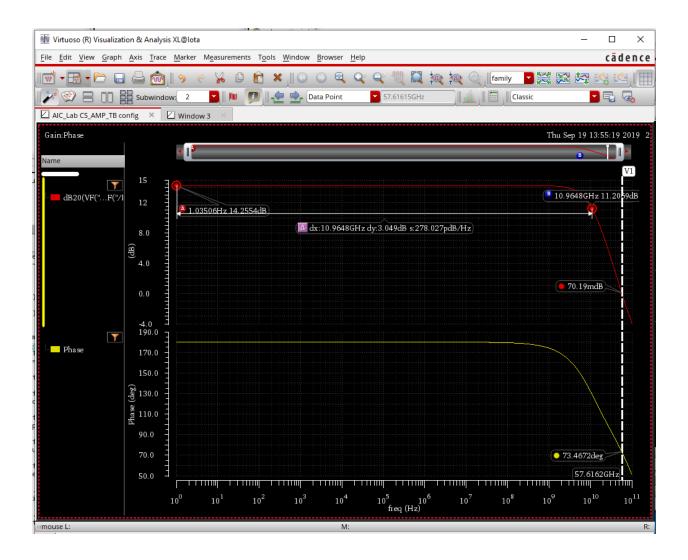

This tutorial briefly introduces the circuit simulation in Cadence. A simple common-source amplifier has been built and simulated step by step using layout entry.

# Layout

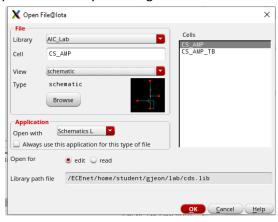

### 1. Open Existing Schematic

- Select "File" in CIW → "Open" to open the existing schematic (Ex: CS AMP).

- $\circ$  You can always manage your libraries by selecting "Tools" in CIW  $\rightarrow$  "Library Manager".

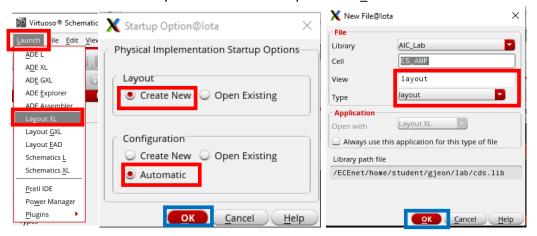

#### 2. Create a Layout

- o After opening the schematic of the commons source amplifier,

- Select "Launch" → "Layout XL" to create a layout for CS\_AMP schematc.

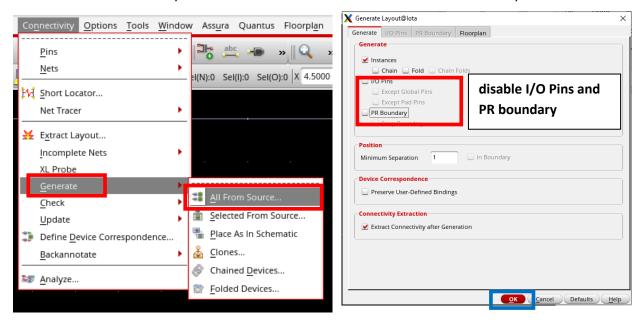

#### 3. Generate Layout from Source

- o After opening the layout windows,

- Select "Connectivity" → "Generate" → "All From Source" to load matched layout from schematic

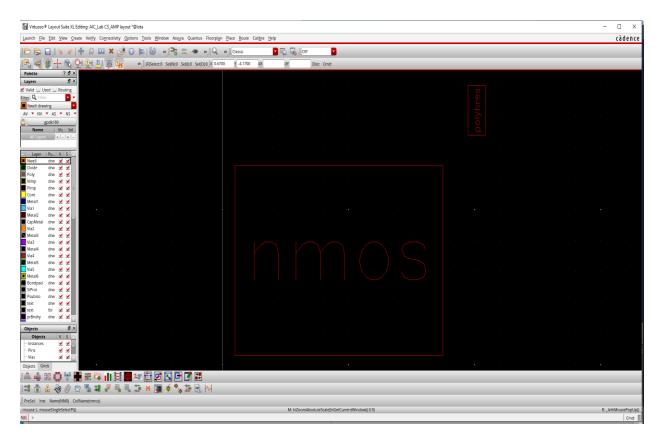

To view layers in the layout windows, press the SHIFT key and the letter F and the layers will be appeared.

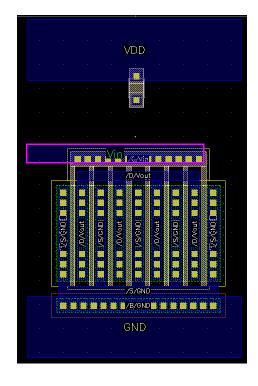

- o Move the resistor in the middle as shown in the figure below.

- $\circ$  Press "Letter M"  $\to$  Click "Resistor"  $\to$  Drag the resistor.

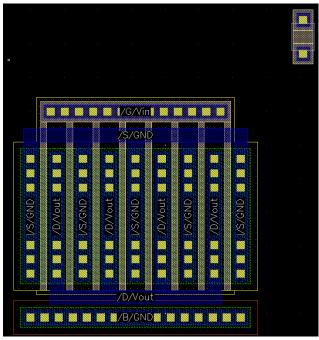

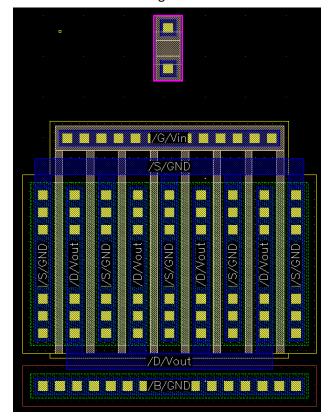

## 4. Relocate Body Layer and Rotate Layout

- To relocate body in the layout,

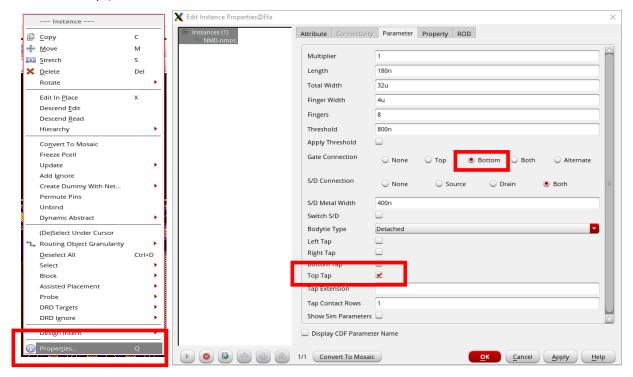

- Select "nMos" → click "right mouse button" → "properties" (shortcut key: Q)

- Change Body to "Top Tap"

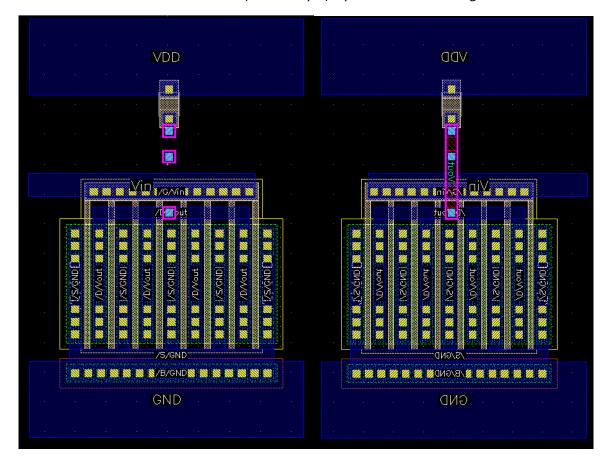

- Rotate the nMOS layer (Select "nMos"  $\rightarrow$  Click "right mouse button"  $\rightarrow$  "Rotate"  $\rightarrow$  "Flip Vertically")

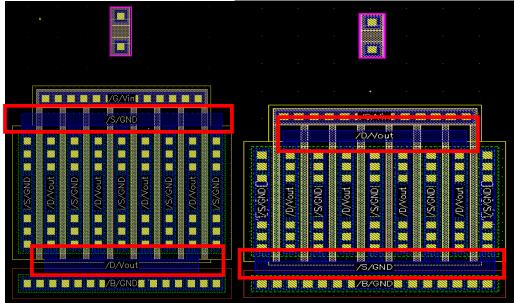

Before

After relocation and Rotation

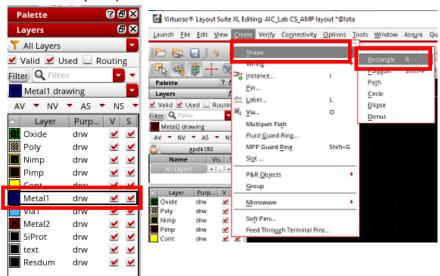

#### 5. Draw Metal 1 Layer

- To draw the metal 1 layer (horizonal layer),

- Select "Metal 1" in layers window  $\rightarrow$  "Create"  $\rightarrow$  "Shape"  $\rightarrow$  "Rectangle" (shortcut key: R)

- $\circ$  Make a large rectangle using left mouse button (Click one point  $\rightarrow$  extend the rectangle  $\rightarrow$  click the another point)

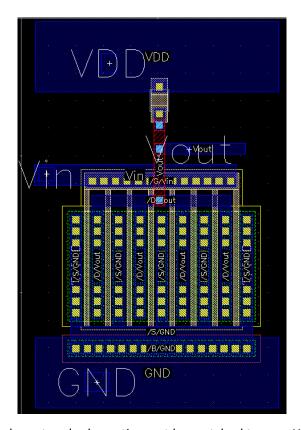

o Draw VDD, GND, and Vin as shown in the figures below.

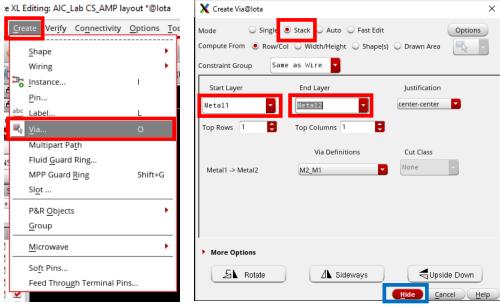

#### 6. Place a Via

- o To place a via (Connection between Metal 1 and Metal 2)

- Select "Create" → "Via" (Shortcut key: O)

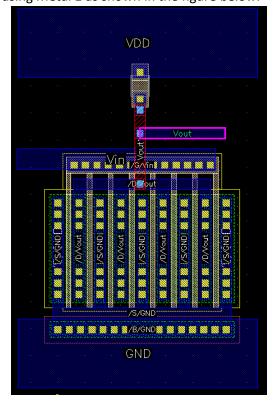

o Place the Vias and draw metal 2 (vertical layer) layer as shown in the figure below.

Draw Vout layer by using Metal 1 as shown in the figure below.

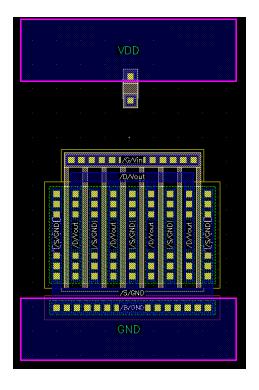

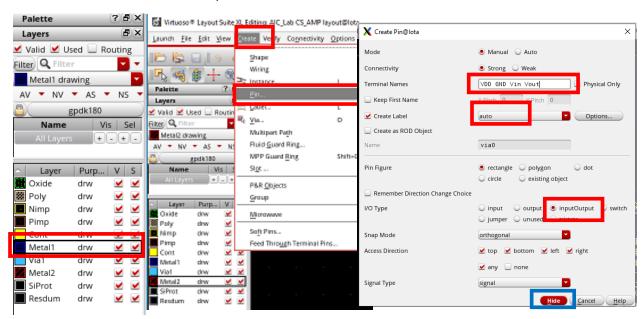

#### 7. Place a Pin

- o To place pins (VDD, GND, Vin, and Vout) in the layout,

- Select "Metal 1" in Layers windows → "Create" → "Pin"

- o Terminal Names: VDD GND Vin Vout

- o Make a rectangle using the left mouse button

- Make sure save the layout

o All pin names in the layout and schematic must be matched to pass LVS.

# Verification

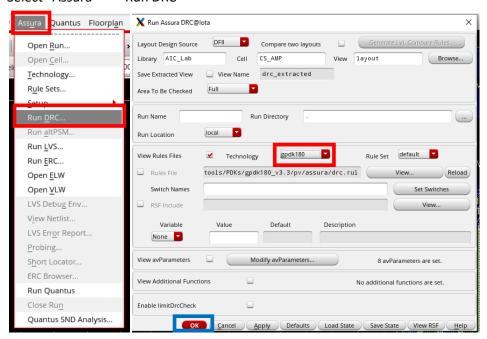

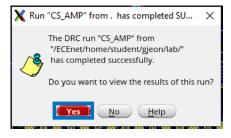

# 1. DRC (Design Rule Check)

- o To check design rule in the layout,

- Select "Assura" → "Run DRC"

o If your layout does not violate any rules, you will get "No DRC errors Found" message.

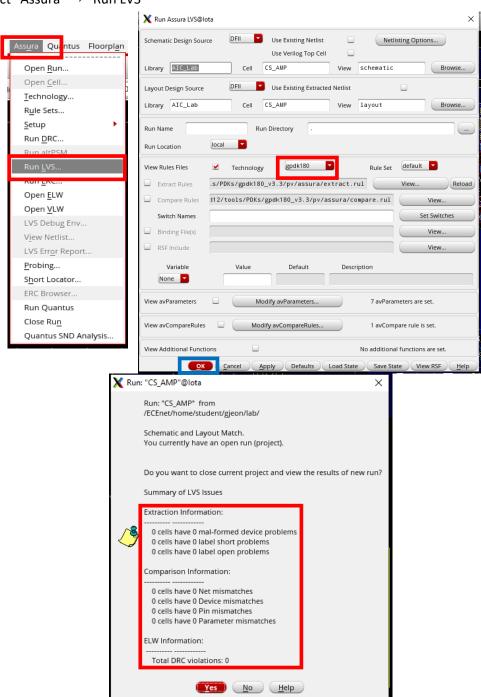

# 2. LVS (Layout VS Schematic)

- o To check LVS simulation,

- Select "Assura" → "Run LVS"

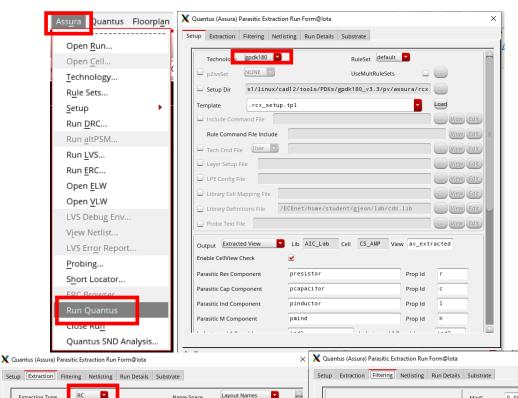

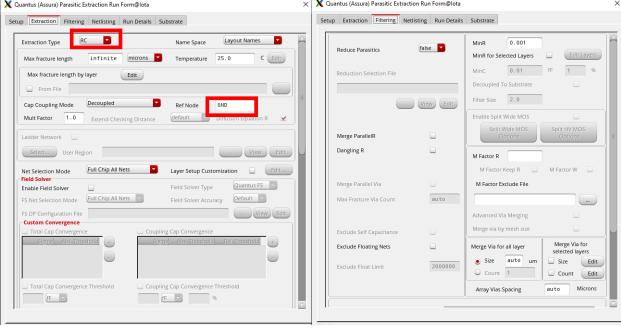

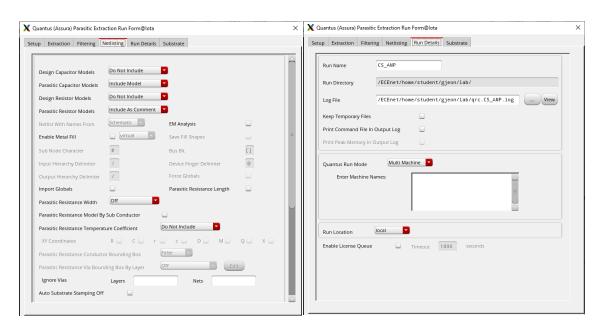

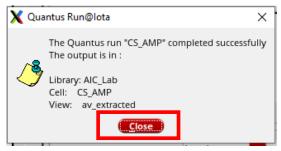

#### 3. Parasitic Extraction (QRC)

- o To extract parasitic RC of the metal layers,

- Select "Assura" → "Run Quantus"

- o After checking all the red boxes, select "Ok"

#### 4. Post-Simulation

- o The parasitic RC are implemented in the av\_extracted.

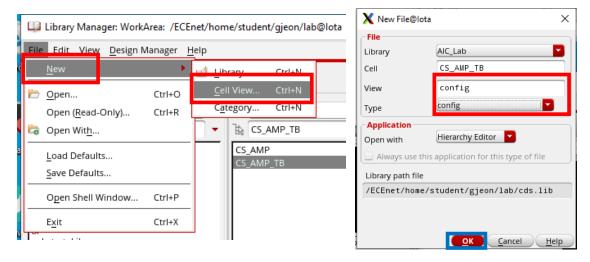

- o To use the parasitic RC in the simulation,

- $\circ$  Select "File" in library manager  $\to$  "New"  $\to$  "Cell View"  $\to$  "config" in the view

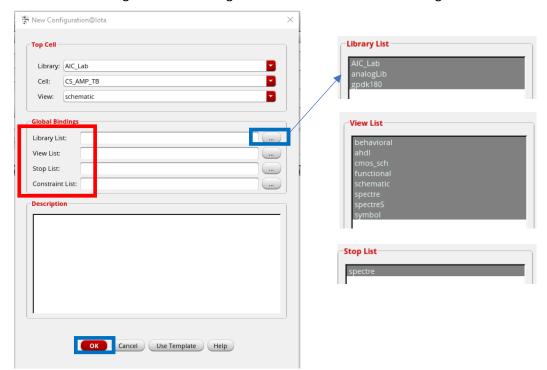

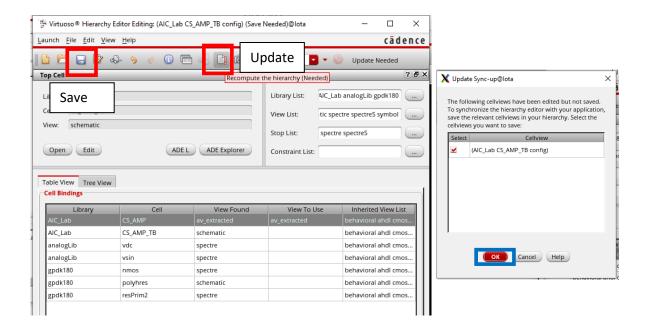

Select following lists in the configuration window as shown in the figure below.

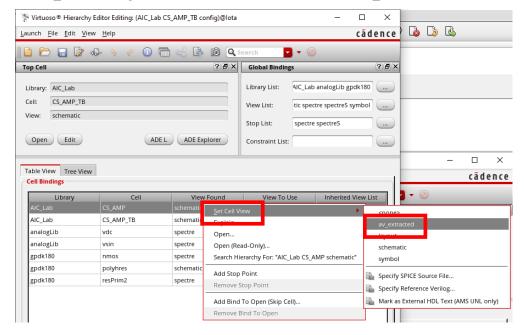

- o All components in the schematic of CS\_AMP\_TB are listed in the table view.

- Change the CS\_AMP from "schematic" to "av\_extracted" view

- Select CS\_AMP → "Right mouse click" → "Set Cell view" → "av\_extracted"

Updates the table view by clicking the icon below and save the configuration

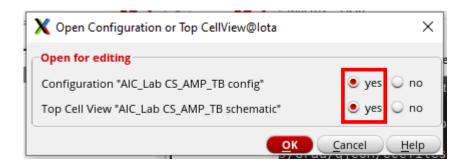

- Close the config window and re-open it

- In library manager, Select "AIC\_Lab(Library)" → "config" in CS\_AMP\_TB

- Two windows, Config and schematic are opened

- Select "Launch" → "ADE L" in schematic window

- o In ADE L window, select "Session" → "Load state"

- Run the simulation in the ADE L, select "Simulation" → "Netlist and Run"