## **Banked Register File for SMT Processors**

Jessica H. Tseng and Krste Asanović **MIT Computer Science and Artificial** Intelligence Laboratory, Cambridge, MA 02139, USA **BARC2004**

#### **Motivation**

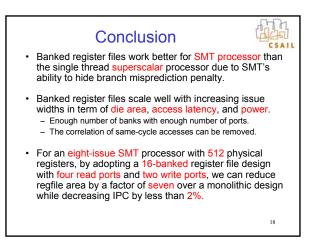

- · Increasing demand on number of ports and number of registers in a register file.

- Growing concerns in access time, power, and die area.

- Example: Alpha 21464 register file (RF) occupied over 5X the area of 64KB primary data cache (DC).

2

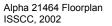

#### **Distributed Architecture** CSAIL Duplicated RF RF - Fewer Read Ports - Same Number of Write Ports Ŵ - Twice Total Number of Registers VALU / - Alpha 21264 & Alpha 21464 luster luster Non-Duplicated RF RF - Fewer Read Ports - Fewer Write Ports

- Complex Inter-Cluster Communication

## **Previous Work**

5

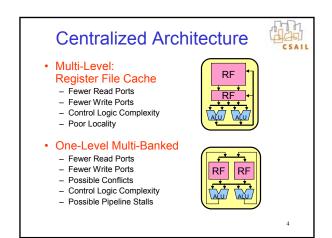

- Use minimal number of ports per register file banks: 1 or 2-read port(s) and 1-write port.

- Avoid issuing instructions that would cause register file read conflicts.

- Add complexity to the critical wakeup-select loop for the issue logic → slower cycle time

- Resolve register file write conflicts by either delaying physical register allocation until write back stage or installing write buffers.

- Complex pipeline control logic

- Possible pipeline stalls

# Our Work

6

- Use more ports per register file bank.

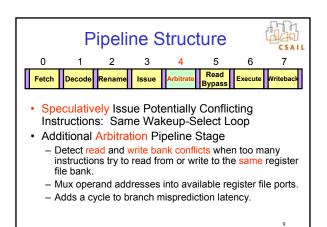

- Speculatively issue potentially conflicting instructions.

- Minimize impact to the critical wakeup-select loop for the issue logic

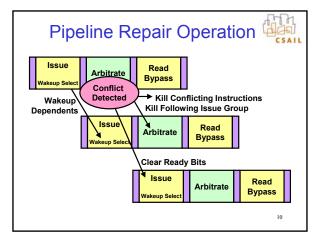

- Rapidly repair pipeline and reissue conflicting instructions when conflicts are detected after issue.

- No write buffer requirement

- No pipeline stalls

Simpler and Faster Control Logic

CSAIL

11

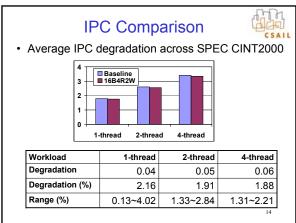

- Increase in branch misprediction latency.

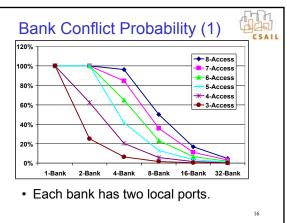

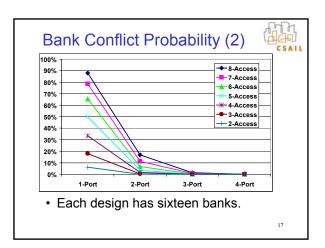

#### Possibility of Bank Conflicts

- Add penalty cycles to repair the pipeline.

- Delay the issuing of dependent instructions.